| 項目 |

仕様 |

| 受信周波数設定 |

①76.0~90.0MHz のいずれか1周波数が標準 (RF 同調部が固定のため)

②RF 同調周波数±1.5MHz の範囲内であれば実用受信範囲

③受信周波数を4つまで設定可能 (従来型チューナのプリセット相当) |

| 受信帯域幅設定 |

以下の4設定が可能 (従来型チューナの IF Band 切換相当)

①236kHz (Super Wide)

②198kHz (Wide) ・・・ 隣接 400kHz 局分離用 [デフォールト設定]

③162kHz (Half)

④126kHz (Narrow) ・・・ 隣接 300kHz 局分離用 |

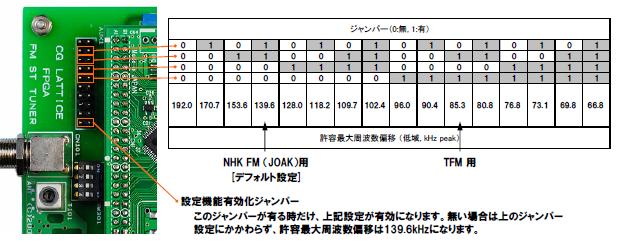

| 許容最大周波数偏移設定 |

①192.0/170.7/153.6/139.6/128.0/118.2/109.7/102.4/96.0/90.4/85.3/80.8/76.8/73.1/69.8/66.8 kHz に設定可能

②139.6kHz がデフォールト

③出力レベルも同時に変わる |

| S/N 比 (80dBf 入力, A 補正) |

82dB |

| 高調波歪率 |

1kHz : 0.002%

10kHz : 0.002% |

| 周波数特性 |

10~15,000Hz +0 -0.2dB |

| ステレオセパレーション |

100Hz : 60dB

1kHz : 60dB

10kHz : 60dB |

| キャリアリーク |

-110dB |

| S/PDIF サンプリングレート |

48/96/192kHz のいずれか/20bit |

| アナログ音声出力 |

L/R ch. 入れ替え機能あり |

| 入出力端子 |

①アンテナ端子 (F 端子)

②光デジタル音声出力 (S/PDIF)

③アナログ音声出力 (RCA ジャック×2)

④電源入力ジャック (2.1mm、センタ+) |

| 電源 |

DC5V 450mA |

| 消費電力 |

2.25W 以下 |

| 外形寸法 |

100(W)×100(H)×35(D)mm (突起部分を含まず) |

| 重量 |

117g |

| 初期設計時期 |

2009年4月 |

| 製作費 |

21,580円 (FPGA 基板が付録の「CQ 出版 ディジタル・デザイン・テクノロジ No.1」と AC アダプタを含む) |

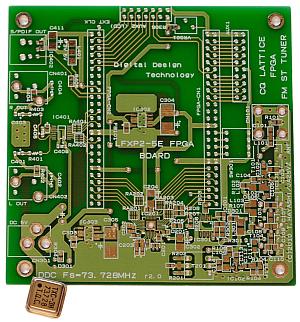

FPGA 基板

FPGA 基板

FM チューナ基板と部品

FM チューナ基板と部品

AC アダプタ

AC アダプタ

2012年6月23日、

FPGA FM Stereo Tuner

の組み立てが完了しました。

2012年6月23日、

FPGA FM Stereo Tuner

の組み立てが完了しました。

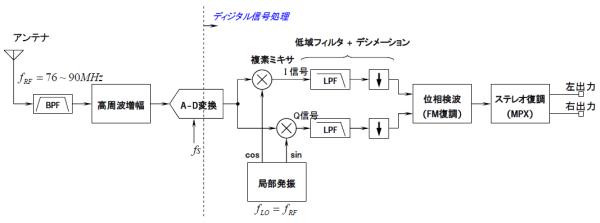

右の図がチューナの論理構成図です。

右の図がチューナの論理構成図です。

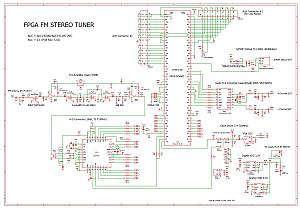

右の図は MPX 部の論理構成です。

右の図は MPX 部の論理構成です。

外観

外観

受信周波数などの設定

受信周波数などの設定

受信帯域幅設定

受信帯域幅設定

許容最大周波数偏移設定

許容最大周波数偏移設定

[アナログ出力左右入れ替え] と [DAI (S/PDIF) サンプリング周波数設定]

[アナログ出力左右入れ替え] と [DAI (S/PDIF) サンプリング周波数設定]

フロントパネルです。

フロントパネルです。

リアパネルです。

リアパネルです。

見る角度を変えてみました。

見る角度を変えてみました。

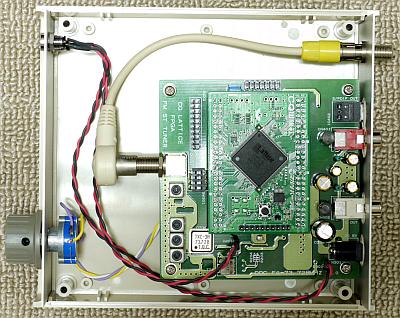

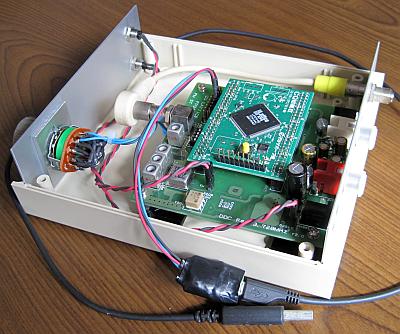

内部の様子です。

内部の様子です。

基板の固定

基板の固定

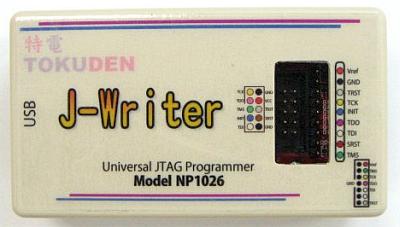

2014年9月28日、

2014年9月28日、

私は FPGA 超初心者なので、うまく動作しない場合に何が悪いのか判断で困るので、まずは動作が保証されている物を使うべきと考えました。

私は FPGA 超初心者なので、うまく動作しない場合に何が悪いのか判断で困るので、まずは動作が保証されている物を使うべきと考えました。